Abstract

In this research paper, a vertical tunnel field-effect transistor (TFET) structure containing a live metal strip and a material with low dielectric constant is designed, and its performance metrics are analyzed in detail. Low-k SiO2 is incorporated in the channel–drain region. A live molybdenum metal strip with low work function is placed in a high-k HfO2 layer in the source–channel region. The device is examined by the parameters Ioff, subthreshold swing, threshold voltage, and Ion/Ioff ratio. The introduction of a live metal strip in the dielectric layer closer to the source–channel interface results in a minimum subthreshold slope and a good Ion/Ioff ratio. The low-k material at the drain reduces the gate-to-drain capacitance. Both the SiO2 layer and the live metal strip show excellent leakage current reduction to 1.4 × 10−17 A/μm. The design provides a subthreshold swing of 5 mV/decade, which is an excellent improvement in TFETs, an on-current of 1.00 × 10−5 A/μm, an Ion/Ioff ratio of 7.14 × 1011, and a threshold voltage of 0.28 V.

Introduction

Rapid miniaturization of electronic devices has led to an increase in leakage current. Leakage current is a big challenge in miniaturized circuits. Miniaturization, at the same time, increased the device performance and reduced the area occupied by the device. The lifetime of devices is reduced because of leakage currents [1]. Leakage increases when thin SiO2 is used as gate dielectric material.

The subthreshold swing (SS) is 60 mV/dec for the thermionic injection of electrons in field-effect transistors (FETs) [2]. In practical implementations, the SS is greater. Thermionic emission affects the off-to-on transition. A small subthreshold swing is needed to turn the device to an off-state sharply, once Vgs drops below the threshold voltage (VT). Tunnel field-effect transistors (TFETs) work based on band-to-band tunneling and not on conventional thermionic emission as the carrier injection mechanism [3]. Band-to-band tunneling enables TFETs to have SS < 60 mV/dec [4-7]. The gate-to-drain capacitance (Cgd) effect (Miller capacitance effect) has an impact on TFET performance. Unwanted effects such as overshoot/undershoot in the inverter characteristics grow when Cgd rises [8]. The gate-to-drain capacitance increases as a result of a high-k material in the drain region [9]. Ambipolar leakage and Miller capacitance are two drawbacks of TFETs. The Miller capacitance can be reduced through oxide overlap and low-bandgap materials [10].

The solution to reduce gate oxide leakage are high-k materials. The device’s ability to keep a charge is increased by using high-k materials, which also aids in downsizing. HfO2 is compatible with a silicon substrate and possesses a high dielectric constant (ε ≈ 25), a large bandgap (5.68 eV), band offsets with silicon, a low leakage current, and a lattice parameter that is close to that of silicon with a modest lattice misfit (ca. 5%) [11].

In this paper, a published VTFET structure is taken for comparison [12]. A large tunnel area and a thin channel enhance the device metrics [13]. In contrast to the previously published model, the proposed design uses a low-k material in the drain region to reduce Cgd. A metal strip with low work function placed at the source–channel interface causes an abrupt change in electron concentration, increasing the tunneling rate [14-18]. Molybdenum, used here as low-work-function live strip (LWLS), has a work function compatible to that of HfO2 [19,20]. The combination of metal strip and high-k material at the drain yields values of Ioff = 1.40 × 10−17, Ion/Ioff ratio = 7.14 × 1011, a reduced subthreshold swing of 5 mV/dec, as well as lower ambipolarity and Miller capacitance.

Impact of dielectric materials on gate source and gate–drain capacitance

The interelectrode capacitance is caused by the dielectric material of the gate. By applying a potential between the capacitor’s electrodes, the charges are polarized [9]. The capacitance of a parallel-plate capacitor is given by

where q, ε0, A, and d are the charge on the plates, the vacuum permittivity, the area of the plates, and the distance between the plates, respectively. The electric field is influenced by voltage, charge, and capacitance. The gradient of voltage that characterizes the electric field between the plates is given by

where dV, dX, V, and d stand for differential voltage, differential length, voltage, and distance between plates, respectively. Instead of SiO2, a high-k dielectric material (HfO2) is used to improve the capacitance by increasing the charge q. The increase in charge results in an increased flow of i(t) in the device. In the drain–channel region, low-k SiO2 is used. This not only reduces the drain region but also reduces the charge held in the parallel-plate capacitor (gate–drain). Hence, it reduces the undesirable Cgd.

Device structure, parameters, and simulation models

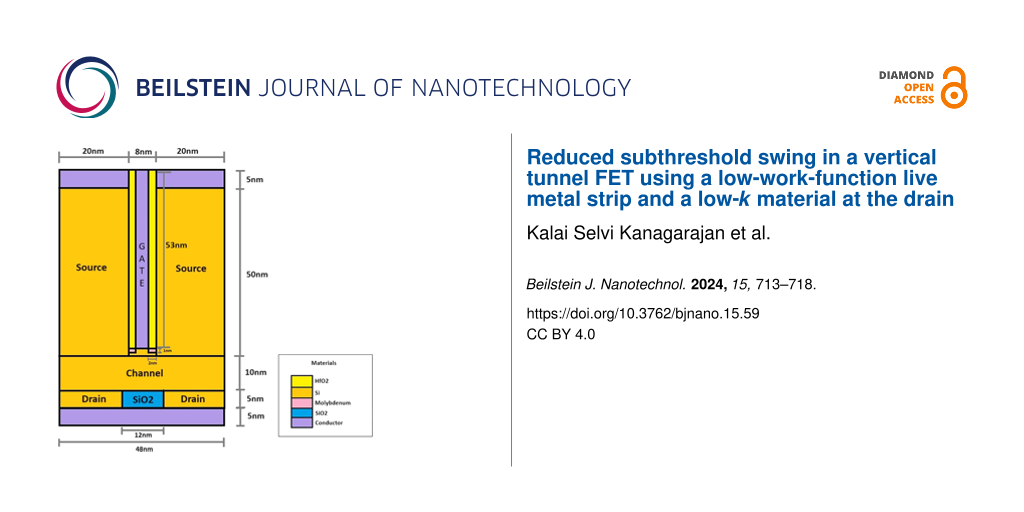

Figure 1 shows the schematic layout of the proposed vertical TFET with dual low-work-function live strip and spacer (VTFET with DLWLS + spacer), which uses molybdenum and low-k SiO2 in the drain region and HfO2 as a high-k dielectric in the source and channel regions. The gate is placed in the middle of the source. The gate length is 8 nm, the gate oxide thickness is 2 nm, and the gate height is 53 nm. The component has a symmetric dual source, measuring 50 nm in height and 20 nm on each side. The drain is 48 nm in length and 5 nm in height. The gate work function is optimized to 3.8 eV. The highly doped source (p++ type), channel (n+ type), and drain (n++ type) materials exhibit doping concentrations of 1 × 1020, 1 × 1017, and 1 × 1019 cm−3, respectively. The molybdenum live metal strip has a length of 2 nm and a height of 1 nm. The drain region is reduced by adding SiO2 to the middle of the drain. Molybdenum is implanted in the oxide layer (HfO2) near the source–channel interface and connected to gate to make it live. The work function of molybdenum is 4.53 eV. Table 1 lists the physical dimensions of the tool used for technology computer-aided design simulations.

![[2190-4286-15-59-1]](/bjnano/content/figures/2190-4286-15-59-1.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 1: Cross-sectional schematic of the proposed VTFET with DLWLS + spacer device.

Figure 1: Cross-sectional schematic of the proposed VTFET with DLWLS + spacer device.

Table 1: Device parameters of the VTFET with DLWLS + spacer.

| source doping (NA) | 1 × 1020 cm−3 |

| drain doping (ND) | 1 × 1019 cm−3 |

| channel doping (NC) | 1 × 1017 cm−3 |

| gate height | 53 nm |

| gate length | 8 nm |

| source height | 50 nm |

| source length | 20 nm |

| drain height | 5 nm |

| drain length | 48 nm |

| channel height | 10 nm |

| channel length | 48 nm |

| gate oxide HfO2 thickness | 2 nm |

| gate work function | 3.8 eV |

| SiO2 thickness | 5 nm |

| SiO2 length | 12 nm |

| LWL length | 2 nm |

| LWL thickness | 1 nm |

| metal strip (molybdenum) work function | 4.53 eV |

The suggested VTFET is compared to the VTFET in [12] to demonstrate the effects of the low-work-function live strip and the low-k material. The device parameters used are listed in Table 1. Reference [12] used bandgap narrowing, Shockley–Read–Hall recombination, Lombardi's mobility model, and band-to-band (non-local) modeling for the simulations. The same models and experimental data have been used for the simulation of proposed structure, and the results are compared.

Results and Discussion

Electron concentration and electric field

The electron concentration for a VTFET with dual low-work-function live strip and a low-k SiO2 spacer at the drain (DLWLS + spacer), a VTFET with dual low-work-function live strip (DLWLS), and a VTFET with a low-k SiO2 spacer at the drain are shown in Figure 2. Compared to the other two designs, the VTFET with DLWLS + spacer has a higher electron concentration. This is because the high-k dielectric gate contains a molybdenum live strip, which raises the electron concentration at the source–channel junction because of its low work function. The rise in electron concentration creates an abrupt change in the source channel. Figure 3 presents the electric field of the VTFET with DLWLS + spacer device. It exhibits a stronger electric field than the other two devices because of the increased number of charge carriers.

![[2190-4286-15-59-2]](/bjnano/content/figures/2190-4286-15-59-2.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 2: Comparison between VTFET with DLWLS + spacer, DLWLS, and spacer regarding electron concentration.

Figure 2: Comparison between VTFET with DLWLS + spacer, DLWLS, and spacer regarding electron concentration.

![[2190-4286-15-59-3]](/bjnano/content/figures/2190-4286-15-59-3.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 3: Comparison between VTFET with DLWLS + spacer, DLWLS, and spacer regarding electric field strength.

Figure 3: Comparison between VTFET with DLWLS + spacer, DLWLS, and spacer regarding electric field strength.

Energy band

Figure 4 shows that the energy barrier is almost the same for VTFET with DLWLS and VTFET with DLWLS + spacer. The energy band diagram of the VTFET with DLWLS and spacer device is shown in Figure 5 for both the on- and the off-state. Compared to the barrier width in the on-state, the distance between valence band of the source and conduction band of the channel is greater in the off-state (Vgs = Vds = 0). In the on-state, Vgs regulates electron motion. A reduction in barrier width enhances electron transfer in the on-state. Leakage current in the off-state is reduced by a wide tunneling barrier.

![[2190-4286-15-59-4]](/bjnano/content/figures/2190-4286-15-59-4.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 4: Comparison between VTFET with DLWLS + spacer, DLWLS, and spacer regarding energy band profile.

Figure 4: Comparison between VTFET with DLWLS + spacer, DLWLS, and spacer regarding energy band profile.

![[2190-4286-15-59-5]](/bjnano/content/figures/2190-4286-15-59-5.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 5: Energy band diagrams of the proposed VTFET with DLWLS + spacer in on-and off-states.

Figure 5: Energy band diagrams of the proposed VTFET with DLWLS + spacer in on-and off-states.

Subthreshold swing

The gate dielectric material and the geometry of the transistor help in reducing the subthreshold swing. The subthreshold swing is 5 mV/dec for VTFET with DLWLS + spacer, 25 mV/dec for DLWLS, and 30 mV/dec for the design with only the spacer. The subthreshold swing of a TFET depends on the high-k gate dielectric and a thin body to assure that the gate field directly modulates the channel. Maximizing the derivative of the junction electric field on the gate–source voltage [4] is another method for reducing the subthreshold voltage swing. Veff is the tunnel–junction bias, ξ is the electric field, a, b are coefficients based on the junction's material characteristics and the device’s cross-sectional area:

Comparison of VTFET with VTFET (DLWLS and Spacer)

The proposed model VTFET with DLWLS + spacer is compared with the previously published work [12]. The Id vs Vgs curve of the model proposed here is better in terms of leakage current as illustrated in Figure 6. The off-current of the proposed model is 1.40 × 10−17 A/μm, while that of the model in [12] is 2.96 × 10−13 A/μm. The threshold voltage is 0.28 V. The on-state current is 1.00 × 10−5 A/μm. The transfer characteristics of the three devices are presented in Figure 7. The leakage current is minimal in the proposed model.

![[2190-4286-15-59-6]](/bjnano/content/figures/2190-4286-15-59-6.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 6: Id vs Vgs of the VTFET with DLWLS + spacer and the model in [12].

Figure 6: Id vs Vgs of the VTFET with DLWLS + spacer and the model in [12].

![[2190-4286-15-59-7]](/bjnano/content/figures/2190-4286-15-59-7.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 7: Comparison between transfer characteristics of VTFET with DLWLS + spacer, DLWLS, and spacer.

Figure 7: Comparison between transfer characteristics of VTFET with DLWLS + spacer, DLWLS, and spacer.

Miller capacitance and leakage

The high dielectric constant of HfO2 increases the capacitance at the source–channel junction. This increases Cgs; however, employing low-k SiO2 at the drain decreases the Miller capacitance, which is desirable for FETs [21]. Figure 8 and Figure 9 show the increase in Cgs and the decrease in Cgd, respectively, for the proposed model. The proposed structure has been simulated with and without dielectric at the drain. The leakage current in presence of the dielectric is 1.40 × 10−17 A/μm, which is small compared to the value without dielectric, which is 5.47 × 10−14 A/μm. Low-k SiO2 reduces the scattering and the charge concentration in the drain region, reduces unwanted capacitance, and acts as a collecting region. The Ion/Ioff value obtained for the proposed structure is 7.14 × 1011. The values for existing structures are 108 to 109. The proposed structure has been designed to have a moderate VT of 0.28 V since FETs with low threshold voltage are used in high-speed designs, but at the cost of higher leakage power consumption. The device previously described in the literature has a low threshold voltage of 0.15 V and a higher off-current than the design proposed here. Hence, the proposed design can be employed in low-power applications.

![[2190-4286-15-59-8]](/bjnano/content/figures/2190-4286-15-59-8.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 8: Capacitance (Cgs)–voltage characteristics of the three models.

Figure 8: Capacitance (Cgs)–voltage characteristics of the three models.

![[2190-4286-15-59-9]](/bjnano/content/figures/2190-4286-15-59-9.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 9: Capacitance (Cgd)–voltage characteristics of the three models.

Figure 9: Capacitance (Cgd)–voltage characteristics of the three models.

Conclusion

In this proposed work, a high-k gate oxide with molybdenum metal is designed along with a low-k material at the drain. FETs are playing a vital role in the IC industry, and low sub-threshold swing and reduced Miller capacitance with low off-state current are required for power-efficient low-leakage memory systems. Hence, a VTFET with a low-work-function live strip and a spacer has been designed for maximum performance by limiting the leakage current. The performance of the proposed VTFET with DLWLS + spacer is presented and compared with standalone DLWLS or spacer structures. Miller capacitance, subthreshold swing, and leakage of the proposed device are improved compared to other architectures because of the low-work-function metal and the low-k material at the drain. The suggested model has been implemented with the help of the Atlas Silvaco tool.

Data Availability Statement

Additional research data is not shared.

References

-

Avci, U. E.; Morris, D. H.; Young, I. A. IEEE J. Electron Devices Soc. 2015, 3, 88–95. doi:10.1109/jeds.2015.2390591

Return to citation in text: [1] -

Ionescu, A. M.; Riel, H. Nature 2011, 479, 329–337. doi:10.1038/nature10679

Return to citation in text: [1] -

Verreck, D.; Groeseneken, G.; Verhulst, A. S. The Tunnel Field-Effect Transistor. In Wiley Encyclopedia of Electrical and Electronics Engineering; Webster,, J. G., Ed.; Wiley: Hoboken, NJ, USA, 2016; pp 1–28. doi:10.1002/047134608x.w8333

Return to citation in text: [1] -

Zhang, Q.; Zhao, W.; Seabaugh, A. IEEE Electron Device Lett. 2006, 27, 297–300. doi:10.1109/led.2006.871855

Return to citation in text: [1] [2] -

Nazir, G.; Rehman, A.; Park, S.-J. ACS Appl. Mater. Interfaces 2020, 12, 47127–47163. doi:10.1021/acsami.0c10213

Return to citation in text: [1] -

Lu, H.; Seabaugh, A. IEEE J. Electron Devices Soc. 2014, 2, 44–49. doi:10.1109/jeds.2014.2326622

Return to citation in text: [1] -

Khatami, Y.; Banerjee, K. IEEE Trans. Electron Devices 2009, 56, 2752–2761. doi:10.1109/ted.2009.2030831

Return to citation in text: [1] -

Mookerjea, S.; Krishnan, R.; Datta, S.; Narayanan, V. IEEE Electron Device Lett. 2009, 30, 1102–1104. doi:10.1109/led.2009.2028907

Return to citation in text: [1] -

Rani, C. S. H.; Bagan, K. B.; Nirmal, D.; Roach, R. S. Silicon 2020, 12, 2337–2343. doi:10.1007/s12633-019-00328-w

Return to citation in text: [1] [2] -

Satyanarayana, B. V. V.; Prakash, M. D. Mater. Today: Proc. 2021, 45, 1997–2001. doi:10.1016/j.matpr.2020.09.420

Return to citation in text: [1] -

Rahou, F. Z.; Bouazza, A. G.; Bouazza, B. J. Nano- Electron. Phys. 2016, 8, 04037. doi:10.21272/jnep.8(4(1)).04037

Return to citation in text: [1] -

Badgujjar, S.; Wadhwa, G.; Singh, S.; Raj, B. Trans. Electr. Electron. Mater. 2020, 21, 74–82. doi:10.1007/s42341-019-00154-2

Return to citation in text: [1] [2] [3] [4] [5] [6] -

Jiang, Z.; Zhuang, Y.; Li, C.; Wang, P.; Liu, Y. J. Semicond. 2016, 37, 094003. doi:10.1088/1674-4926/37/9/094003

Return to citation in text: [1] -

Chandan, B. V.; Nigam, K.; Tirkey, S.; Sharma, D. Appl. Phys. A: Mater. Sci. Process. 2019, 125, No. 665. doi:10.1007/s00339-019-2966-1

Return to citation in text: [1] -

Kumar, S.; Singh, K. S.; Nigam, K.; Chaturvedi, S. Silicon 2021, 13, 2065–2070. doi:10.1007/s12633-020-00601-3

Return to citation in text: [1] -

Yadav, S.; Lemtur, A.; Sharma, D.; Aslam, M.; Soni, D. Micro Nano Lett. 2018, 13, 1469–1474. doi:10.1049/mnl.2018.5072

Return to citation in text: [1] -

Nigam, K.; Kondekar, P.; Chandan, B. V.; Kumar, S.; Tikkiwal, V. A.; Dharmender; Singh, K. S.; Bhardwaj, E.; Choubey, S.; Chaturvedi, S. Silicon 2022, 14, 1549–1558. doi:10.1007/s12633-021-00958-z

Return to citation in text: [1] -

Lin, R.; Lu, Q.; Ranade, P.; King, T. J.; Hu, C. IEEE Electron Device Lett. 2002, 23, 49–51. doi:10.1109/55.974809

Return to citation in text: [1] -

Ranade, P.; Takeuchi, H.; King, T.-J.; Hu, C. Electrochem. Solid-State Lett. 2001, 4, G85. doi:10.1149/1.1402497

Return to citation in text: [1] -

Lu, J.; Kuo, Y.; Chatterjee, S.; Tewg, J. Y. J. Vac. Sci. Technol., B: Microelectron. Nanometer Struct.–Process., Meas., Phenom. 2006, 24, 349. doi:10.1116/1.2163883

Return to citation in text: [1] -

Selvi, K.; Dhanalakshmi, K. S. Performance Optimization in Recessed Modified Junctionless FET. IEEE 6th International Conference on Trends in Electronics and Informatics (ICOEI); 2022; pp 255–260. doi:10.1109/icoei53556.2022.9777109

Return to citation in text: [1]

| 12. | Badgujjar, S.; Wadhwa, G.; Singh, S.; Raj, B. Trans. Electr. Electron. Mater. 2020, 21, 74–82. doi:10.1007/s42341-019-00154-2 |

| 12. | Badgujjar, S.; Wadhwa, G.; Singh, S.; Raj, B. Trans. Electr. Electron. Mater. 2020, 21, 74–82. doi:10.1007/s42341-019-00154-2 |

| 12. | Badgujjar, S.; Wadhwa, G.; Singh, S.; Raj, B. Trans. Electr. Electron. Mater. 2020, 21, 74–82. doi:10.1007/s42341-019-00154-2 |

| 1. | Avci, U. E.; Morris, D. H.; Young, I. A. IEEE J. Electron Devices Soc. 2015, 3, 88–95. doi:10.1109/jeds.2015.2390591 |

| 8. | Mookerjea, S.; Krishnan, R.; Datta, S.; Narayanan, V. IEEE Electron Device Lett. 2009, 30, 1102–1104. doi:10.1109/led.2009.2028907 |

| 12. | Badgujjar, S.; Wadhwa, G.; Singh, S.; Raj, B. Trans. Electr. Electron. Mater. 2020, 21, 74–82. doi:10.1007/s42341-019-00154-2 |

| 4. | Zhang, Q.; Zhao, W.; Seabaugh, A. IEEE Electron Device Lett. 2006, 27, 297–300. doi:10.1109/led.2006.871855 |

| 5. | Nazir, G.; Rehman, A.; Park, S.-J. ACS Appl. Mater. Interfaces 2020, 12, 47127–47163. doi:10.1021/acsami.0c10213 |

| 6. | Lu, H.; Seabaugh, A. IEEE J. Electron Devices Soc. 2014, 2, 44–49. doi:10.1109/jeds.2014.2326622 |

| 7. | Khatami, Y.; Banerjee, K. IEEE Trans. Electron Devices 2009, 56, 2752–2761. doi:10.1109/ted.2009.2030831 |

| 4. | Zhang, Q.; Zhao, W.; Seabaugh, A. IEEE Electron Device Lett. 2006, 27, 297–300. doi:10.1109/led.2006.871855 |

| 3. | Verreck, D.; Groeseneken, G.; Verhulst, A. S. The Tunnel Field-Effect Transistor. In Wiley Encyclopedia of Electrical and Electronics Engineering; Webster,, J. G., Ed.; Wiley: Hoboken, NJ, USA, 2016; pp 1–28. doi:10.1002/047134608x.w8333 |

| 9. | Rani, C. S. H.; Bagan, K. B.; Nirmal, D.; Roach, R. S. Silicon 2020, 12, 2337–2343. doi:10.1007/s12633-019-00328-w |

| 12. | Badgujjar, S.; Wadhwa, G.; Singh, S.; Raj, B. Trans. Electr. Electron. Mater. 2020, 21, 74–82. doi:10.1007/s42341-019-00154-2 |

| 12. | Badgujjar, S.; Wadhwa, G.; Singh, S.; Raj, B. Trans. Electr. Electron. Mater. 2020, 21, 74–82. doi:10.1007/s42341-019-00154-2 |

| 14. | Chandan, B. V.; Nigam, K.; Tirkey, S.; Sharma, D. Appl. Phys. A: Mater. Sci. Process. 2019, 125, No. 665. doi:10.1007/s00339-019-2966-1 |

| 15. | Kumar, S.; Singh, K. S.; Nigam, K.; Chaturvedi, S. Silicon 2021, 13, 2065–2070. doi:10.1007/s12633-020-00601-3 |

| 16. | Yadav, S.; Lemtur, A.; Sharma, D.; Aslam, M.; Soni, D. Micro Nano Lett. 2018, 13, 1469–1474. doi:10.1049/mnl.2018.5072 |

| 17. | Nigam, K.; Kondekar, P.; Chandan, B. V.; Kumar, S.; Tikkiwal, V. A.; Dharmender; Singh, K. S.; Bhardwaj, E.; Choubey, S.; Chaturvedi, S. Silicon 2022, 14, 1549–1558. doi:10.1007/s12633-021-00958-z |

| 18. | Lin, R.; Lu, Q.; Ranade, P.; King, T. J.; Hu, C. IEEE Electron Device Lett. 2002, 23, 49–51. doi:10.1109/55.974809 |

| 11. | Rahou, F. Z.; Bouazza, A. G.; Bouazza, B. J. Nano- Electron. Phys. 2016, 8, 04037. doi:10.21272/jnep.8(4(1)).04037 |

| 19. | Ranade, P.; Takeuchi, H.; King, T.-J.; Hu, C. Electrochem. Solid-State Lett. 2001, 4, G85. doi:10.1149/1.1402497 |

| 20. | Lu, J.; Kuo, Y.; Chatterjee, S.; Tewg, J. Y. J. Vac. Sci. Technol., B: Microelectron. Nanometer Struct.–Process., Meas., Phenom. 2006, 24, 349. doi:10.1116/1.2163883 |

| 10. | Satyanarayana, B. V. V.; Prakash, M. D. Mater. Today: Proc. 2021, 45, 1997–2001. doi:10.1016/j.matpr.2020.09.420 |

| 21. | Selvi, K.; Dhanalakshmi, K. S. Performance Optimization in Recessed Modified Junctionless FET. IEEE 6th International Conference on Trends in Electronics and Informatics (ICOEI); 2022; pp 255–260. doi:10.1109/icoei53556.2022.9777109 |

| 9. | Rani, C. S. H.; Bagan, K. B.; Nirmal, D.; Roach, R. S. Silicon 2020, 12, 2337–2343. doi:10.1007/s12633-019-00328-w |

| 13. | Jiang, Z.; Zhuang, Y.; Li, C.; Wang, P.; Liu, Y. J. Semicond. 2016, 37, 094003. doi:10.1088/1674-4926/37/9/094003 |

© 2024 Kanagarajan and Sadhasivan; licensee Beilstein-Institut.

This is an open access article licensed under the terms of the Beilstein-Institut Open Access License Agreement (https://www.beilstein-journals.org/bjnano/terms), which is identical to the Creative Commons Attribution 4.0 International License (https://creativecommons.org/licenses/by/4.0). The reuse of material under this license requires that the author(s), source and license are credited. Third-party material in this article could be subject to other licenses (typically indicated in the credit line), and in this case, users are required to obtain permission from the license holder to reuse the material.